|

omdl

v1.0

OpenSCAD Mechanical Design Library

|

|

omdl

v1.0

OpenSCAD Mechanical Design Library

|

PCI Express expansion chassis and/or enclosure generator. More...

Collaboration diagram for PCIe Expansion:

Collaboration diagram for PCIe Expansion:Files | |

| file | pcie_expansion.scad |

| A PCI Express expansion chassis and/or enclosure generator. | |

Configuration: PCI-E standard | |

| pcie_spec_common | |

| pcie_spec_full | |

| pcie_spec_half | |

Configuration: Riser board | |

| riser_PCE164P_NO3_VER_007 | |

| <map> USB 3.0 PCE164P-NO3 VER 007 1-slot riser board. More... | |

| riser_AAAPCIE4HUB | |

| <map> AAAPCIE4HUB multiplier HUB 4-slot riser board. More... | |

| riser_SFF_8612_4X_to_PCI_E_16X | |

| <map> SFF-8612 4X lane to 16X 1-slot riser board. More... | |

Configuration: Enclosure | |

| enclosure_def | |

| <map> Default enclosure configuration. More... | |

Variables | |

| pcie_expansion_debug = false | |

| <boolean> Set to true to check configuration structure. | |

| pcie_expansion_debug_verbose = false | |

| <boolean> Set to true for verbose configuration checking. | |

| riser_pcb_def = riser_PCE164P_NO3_VER_007 | |

| <map> Default riser board configuration. | |

Functions | |

| function | pcie_expansion_rb_size (riser_pcb, vslots) |

| Get riser board size for riser configuration. More... | |

| function | pcie_expansion_size (pcie_base=pcie_spec_common, pcie_form=pcie_spec_half, riser_pcb=riser_pcb_def, enclosure=enclosure_def, riser_pcb_width, external=false) |

| Get enclosure internal or external size. More... | |

| function | pcie_expansion_rbs_keys (pcie_base=pcie_spec_common, pcie_form=pcie_spec_half, riser_pcb=riser_pcb_def, enclosure=enclosure_def, riser_pcb_width, enclosure_size, center_w=true, zero_lh=false, edge1_w=false, adjust_h=false) |

| Get list of slot key locations of all riser boards. More... | |

Modules | |

| module | pcie_expansion (pcie_base=pcie_spec_common, pcie_form=pcie_spec_half, riser_pcb=riser_pcb_def, enclosure=enclosure_def, show_riser=false, part_color, part=7, mode=3, verb=0) |

| Generate a PCI Express expansion open chassis or closed enclosure. More... | |

PCI Express expansion chassis and/or enclosure generator.

| Requires: |

|---|

| include <omdl-base.scad>; |

| include <shapes/select_common_2d.scad>; |

| include <shapes/select_common_3d.scad>; |

| include <transforms/base_cs.scad>; |

| include <transforms/layout.scad>; |

| include <models/2d/joint/dovetail.scad>; |

| include <parts/3d/fastener/clamps.scad>; |

| include <parts/3d/enclosure/project_box_rectangle.scad>; |

| include <parts/3d/computer/pcie_expansion.scad>; |

| function pcie_expansion_rb_size | ( | riser_pcb | , |

| vslots | |||

| ) |

Get riser board size for riser configuration.

| riser_pcb | <map> The riser board configuration. |

| slots | <integer> Optional slot count override. |

Here is the caller graph for this function:

Here is the caller graph for this function:| function pcie_expansion_size | ( | pcie_base | = pcie_spec_common, |

| pcie_form | = pcie_spec_half, |

||

| riser_pcb | = riser_pcb_def, |

||

| enclosure | = enclosure_def, |

||

| riser_pcb_width | , | ||

| external | = false |

||

| ) |

Get enclosure internal or external size.

| pcie_base | <map> PCI-E standard common configuration. |

| pcie_form | <map> PCI-E half or full configuration. |

| riser_pcb | <map> The riser board configuration. |

| enclosure | <map> The enclosure design configuration. |

| riser_pcb_width | <decimal> The riser board width. |

| external | <boolean> Set true to return external size and false for internal size. |

Here is the caller graph for this function:

Here is the caller graph for this function:| function pcie_expansion_rbs_keys | ( | pcie_base | = pcie_spec_common, |

| pcie_form | = pcie_spec_half, |

||

| riser_pcb | = riser_pcb_def, |

||

| enclosure | = enclosure_def, |

||

| riser_pcb_width | , | ||

| enclosure_size | , | ||

| center_w | = true, |

||

| zero_lh | = false, |

||

| edge1_w | = false, |

||

| adjust_h | = false |

||

| ) |

Get list of slot key locations of all riser boards.

| pcie_base | <map> PCI-E standard common configuration. |

| pcie_form | <map> PCI-E half or full configuration. |

| riser_pcb | <map> The riser board configuration. |

| enclosure | <map> The enclosure design configuration. |

| riser_pcb_width | <decimal> The riser board width. |

| enclosure_size | <decimal-list-3> The enclosure's internal size. |

| center_w | <boolean> Use center of the enclosure as zero for the widths. |

| zero_lh | <boolean> Zero the lengths and heights for each slot location, corresponding to the enclosure location [center, bottom]. |

| edge1_w | <boolean> The initial offset is for each riser board edge-1 rather than the slot-1 for board edge identification. |

| adjust_h | <boolean> Adjust all heights by the offset of the enclosure sides and cover relative to the base when assembled. |

Here is the call graph for this function:

Here is the call graph for this function: Here is the caller graph for this function:

Here is the caller graph for this function:| module pcie_expansion | ( | pcie_base | = pcie_spec_common, |

| pcie_form | = pcie_spec_half, |

||

| riser_pcb | = riser_pcb_def, |

||

| enclosure | = enclosure_def, |

||

| show_riser | = false, |

||

| part_color | , | ||

| part | = 7, |

||

| mode | = 3, |

||

| verb | = 0 |

||

| ) |

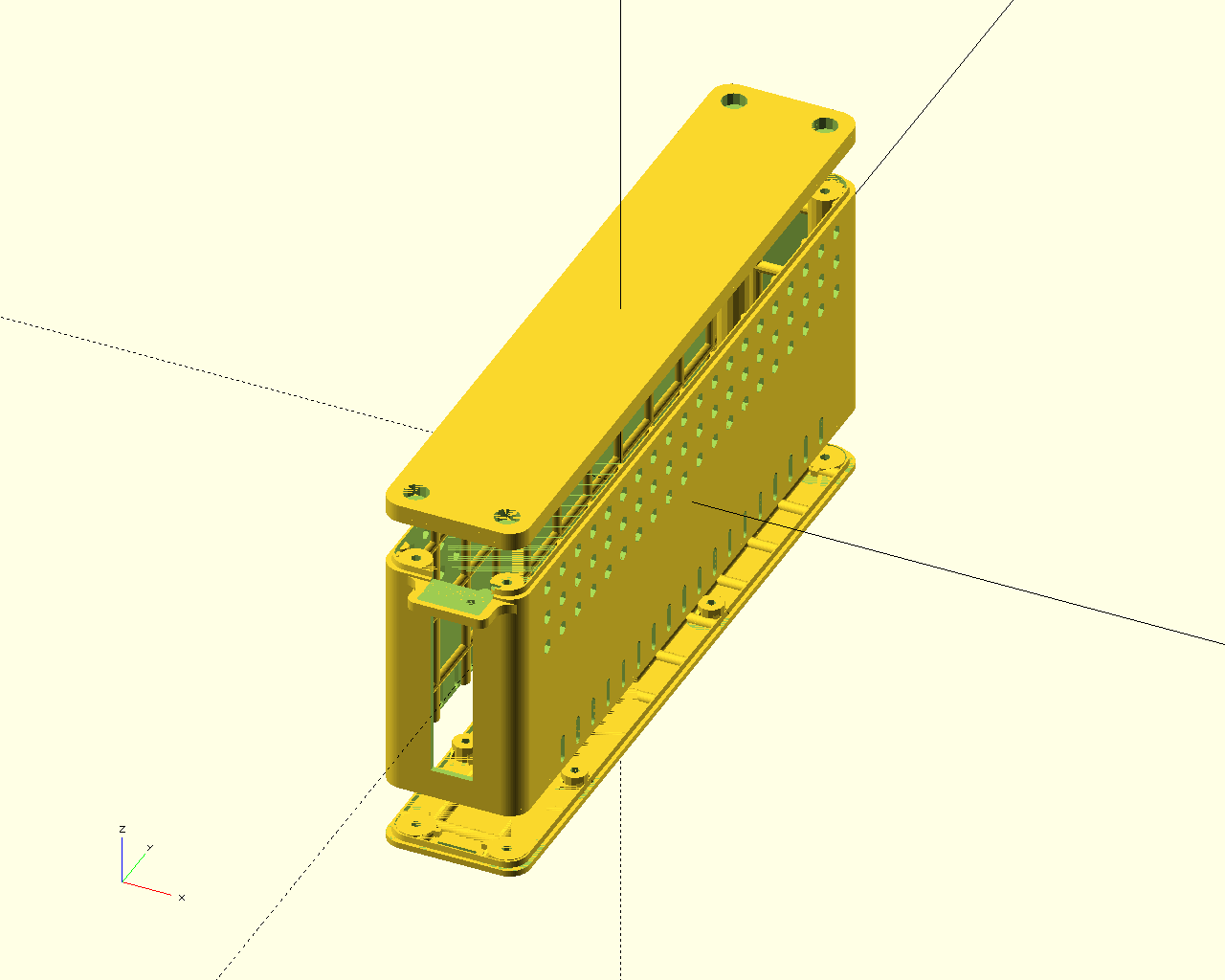

Generate a PCI Express expansion open chassis or closed enclosure.

| pcie_base | <map> PCI-E standard common configuration. |

| pcie_form | <map> PCI-E half or full configuration. |

| riser_pcb | <map> The riser board configuration. |

| enclosure | <map> The enclosure design configuration. |

| show_riser | <boolean> Render model of riser board on the enclosure base. |

| part_color | <color-list-6> a list of colors for each part; [base, sides, cover, ...]. |

| part | <integer> The part to construct; A binary encoded integer value (see below). |

| mode | <integer> The construction orientation mode with (0=design, 1=print, 2=assembled, 3=exploded, 4=build-plate). |

| verb | <integer> The output console verbosity. |

This module is designed to construct chassis and enclosures for common Peripheral Component Interconnect Express (PCIe) riser boards, which provide external access to PCIe slots. These riser boards are commonly used to connect one or more GPUs, or other PCIe cards, externally to a computer system. The module offers the capability to generate both open chassis and closed enclosures.

Integer value is binary encoded.

| b | description |

|---|---|

| 0 | base |

| 1 | sides with in-place bracket mount tab shelf |

| 2 | cover |

| 3 | sides with female dovetails for use with separate mount tab |

| 4 | separate bracket mount tab with male dovetails |

| 5 | mount tab dovetail joint test assembly (design mode) |

| 6 | mount tab dovetail joint test build plate for fabrication |

Before fabricating a design that includes a dovetailed bracket mount tab, create and assemble a dovetail test joint to verify proper fit. Enable the test joint by setting part bit 6 to 1 (for example, part = pow(2, 6)). To refine or evaluate the dovetail configuration, model an assembled test joint by enabling part bit 5.

Enclosure customization example script

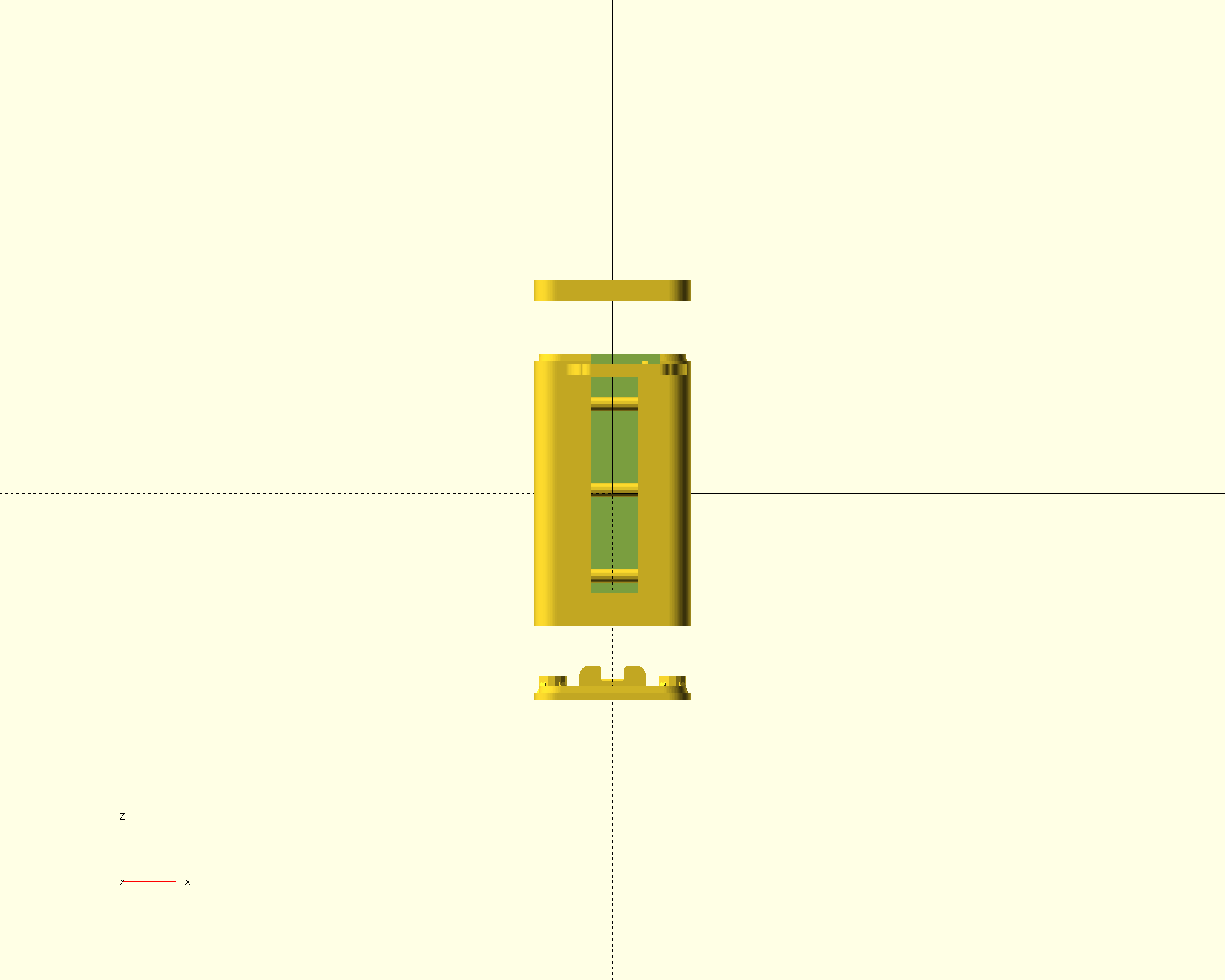

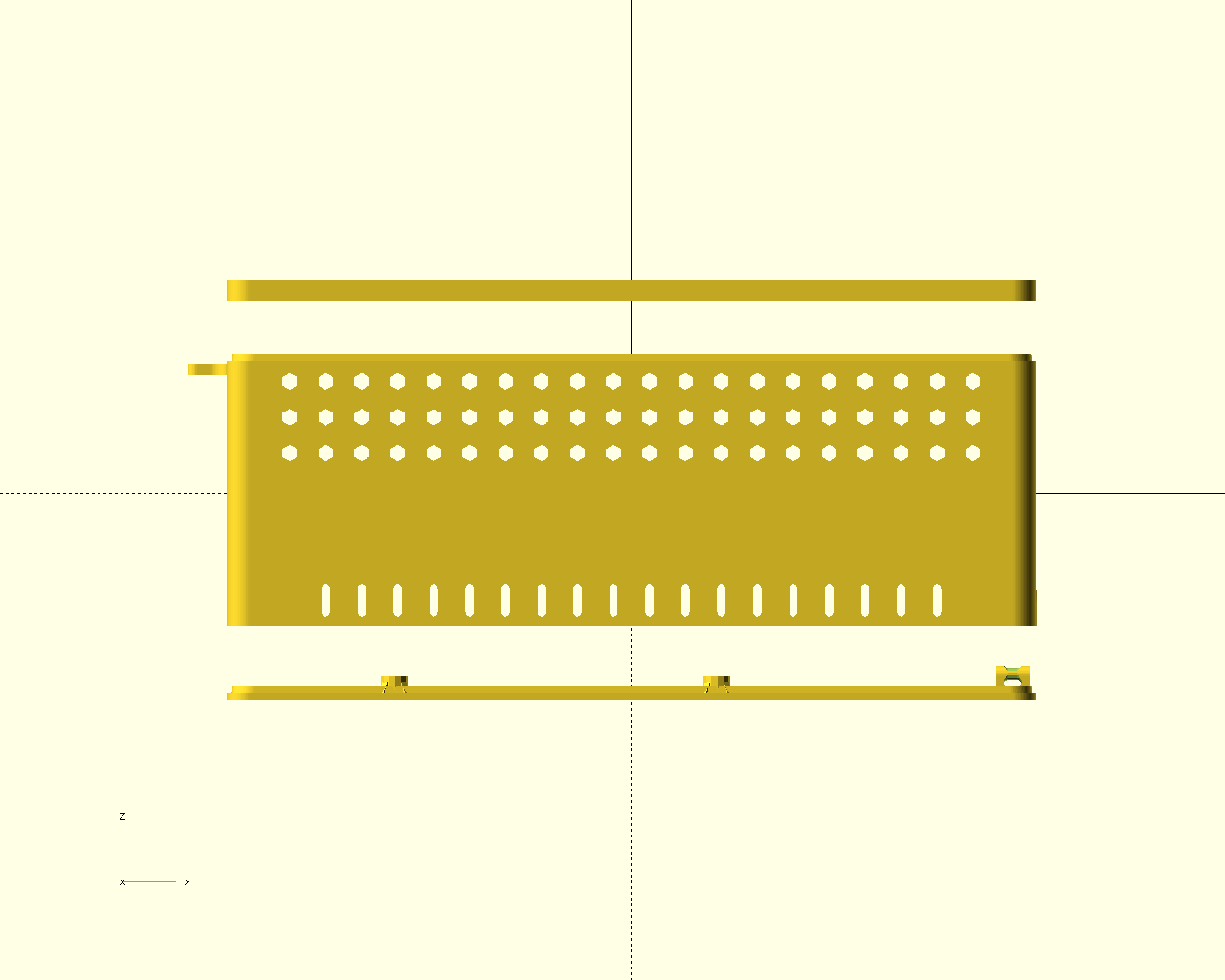

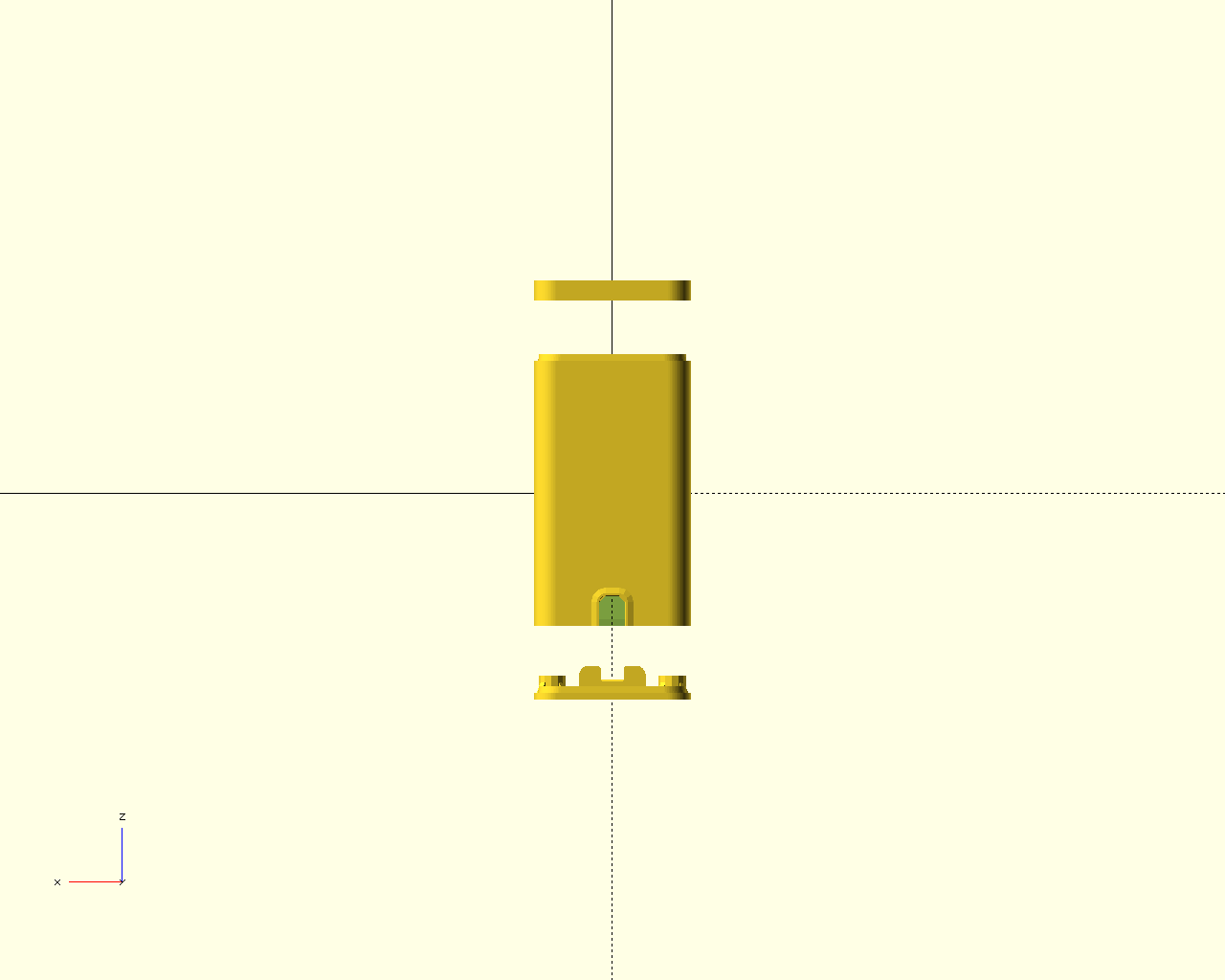

| front | right | back | diag |

|---|---|---|---|

|  |  |  |

Definition at line 1686 of file pcie_expansion.scad.

Here is the call graph for this function:

Here is the call graph for this function:| pcie_spec_common |

<map> PCI-E standard specifications common to full and half-length cards.

Definition at line 174 of file pcie_expansion.scad.

| pcie_spec_full |

<map> PCI-E full-length card standard specifications.

Definition at line 192 of file pcie_expansion.scad.

| pcie_spec_half |

<map> PCI-E half-length card standard specifications.

Definition at line 211 of file pcie_expansion.scad.

| riser_PCE164P_NO3_VER_007 |

<map> USB 3.0 PCE164P-NO3 VER 007 1-slot riser board.

A configuration for the PCE164P-NO3 VER 007 1-slot riser board. This is the default riser board and can be used as a basis for constructing new riser board configuration.

Riser board configuration table

| key | value | description |

|---|---|---|

| bottom_clearance | 3 | Vertical clearance under riser board |

| mount_holes | [[-11.5, -11], [24.5, -11], [-11.5, 85.5], [24.5, 85.5]] | Riser board mount holes; referenced to slot-1 key |

| mount_holes_add | undef | Riser board mount holes additions |

| multi_slot_offset | 20.32 | PCI-E multi-slot, slot-to-slot spacing |

| pcb_length | 127.75 | Riser board PCB length front to rear |

| pcb_th | 1.75 | Riser board PCB thickness |

| post_fins | [4] | Mount post fin configuration: see project_box_rectangle() |

| post_hole_d | 3 | Mount post hole diameter |

| post_pad_d | 8.25 | Mount post diameter |

| post_rotate | 45 | Mount post rotation in degrees |

| slot1_to_edge1 | 15 | Riser board slot-1 to adjacent edge distance |

| slot_count | 1 | Riser physical slot count (fixed) |

| slot_key_to_edgef | 113.25 | Riser board key to front edge distance |

| slot_link_width | 16 | Slot connector link width {1|4|8|16} |

| slotn_to_edgen | 28 | Riser board slot-n to adjacent edge distance |

| vslot_count | 0 | Riser virtual slot count (user adjustable) |

Definition at line 371 of file pcie_expansion.scad.

| riser_AAAPCIE4HUB |

<map> AAAPCIE4HUB multiplier HUB 4-slot riser board.

A configuration for the AAAPCIE4HUB multiplier HUB 1-slot riser board.

Riser board configuration table

| key | value | description |

|---|---|---|

| bottom_clearance | 3 | Vertical clearance under riser board |

| mount_holes | [[-9, -7], [11, -7], [68, -7], [-9, 39], [11, 39], [68, 39]] | Riser board mount holes; referenced to slot-1 key |

| mount_holes_add | undef | Riser board mount holes additions |

| multi_slot_offset | 20.32 | PCI-E multi-slot, slot-to-slot spacing |

| pcb_length | 99 | Riser board PCB length front to rear |

| pcb_th | 1.5 | Riser board PCB thickness |

| post_fins | [4] | Mount post fin configuration: see project_box_rectangle() |

| post_hole_d | 3 | Mount post hole diameter |

| post_pad_d | 8.25 | Mount post diameter |

| post_rotate | 45 | Mount post rotation in degrees |

| slot1_to_edge1 | 12 | Riser board slot-1 to adjacent edge distance |

| slot_count | 4 | Riser physical slot count (fixed) |

| slot_key_to_edgef | 74 | Riser board key to front edge distance |

| slot_link_width | 1 | Slot connector link width {1|4|8|16} |

| slotn_to_edgen | 12 | Riser board slot-n to adjacent edge distance |

| vslot_count | 0 | Riser virtual slot count (user adjustable) |

Definition at line 520 of file pcie_expansion.scad.

| riser_SFF_8612_4X_to_PCI_E_16X |

<map> SFF-8612 4X lane to 16X 1-slot riser board.

A configuration for the SFF-8612 4X lane to 16X 1-slot riser board.

Riser board configuration table

| key | value | description |

|---|---|---|

| bottom_clearance | 0 | Vertical clearance under riser board |

| mount_holes | [[-3, -29], [34, -29], [-3, 87], [34, 87]] | Riser board mount holes; referenced to slot-1 key |

| mount_holes_add | undef | Riser board mount holes additions |

| multi_slot_offset | 20.32 | PCI-E multi-slot, slot-to-slot spacing |

| pcb_length | 122 | Riser board PCB length front to rear |

| pcb_th | 1.75 | Riser board PCB thickness |

| post_fins | [4] | Mount post fin configuration: see project_box_rectangle() |

| post_hole_d | 2.75 | Mount post hole diameter |

| post_pad_d | 7.5625 | Mount post diameter |

| post_rotate | 45 | Mount post rotation in degrees |

| slot1_to_edge1 | 5.75 | Riser board slot-1 to adjacent edge distance |

| slot_count | 1 | Riser physical slot count (fixed) |

| slot_key_to_edgef | 89.5 | Riser board key to front edge distance |

| slot_link_width | 16 | Slot connector link width {1|4|8|16} |

| slotn_to_edgen | 37 | Riser board slot-n to adjacent edge distance |

| vslot_count | 0 | Riser virtual slot count (user adjustable) |

Definition at line 672 of file pcie_expansion.scad.

| enclosure_def |

<map> Default enclosure configuration.

The default enclosure configuration map.

Default enclosure configuration table

| key | value | description |

|---|---|---|

| board_count | 1 | Enclosure riser board count |

| bracket_mount_tab | [3.25, 4, 3.125, [3, 3, 5, 5], [1, 1, 4, 3], [5, 6, 2, 0.75, 0.25]] | Bracket mount tab configuration |

| bracket_shoe_gap_p | 0.25 | Bracket shoe gap% [w, l, h] |

| bracket_shoe_offset | -2 | Bracket shoe vertical offset [h] |

| bracket_window_gap | 2 | Bracket connector window gap [w] |

| clamps_base | [[[[7, 4.75], [5.5, 2.25], [20, 10, 10], [3, [0], 10, [0, -1], [0, -0.25]], [3, 1, 1.25], undef], [[[0, 1], 0, 1, [0, 0], [true, 5.04688, [1, 2.5, 0.5, 31]]]]]] | Enclosure base clamps: see clamp_zt_1p() |

| cut_sides | [[18, 12, 10, 10], [10, 15, 0, 0], [1, 4, 0, 0]] | Enclosure sides cut [insets, vr, vrm] |

| holes_base | undef | Enclosure base hole instances: see project_box_rectangle() |

| holes_cover | undef | Enclosure cover hole instances: see project_box_rectangle() |

| holes_sides | [[[2, [2.5, 6]], -1, [0, [0, 0, 0.5], [90, 0, 90], 0, 30, [0, -10], [20, 3], [10.75, -10.75], [true, false]]], [[3, [2.5, 10], 1.5], -1, [0, [0, 0, -0.5], [90, 0, 90], 0, 0, [0, 5.5], 18, 10.75, true]]] | Enclosure side hole instances: see project_box_rectangle() |

| lips_base | 1 | Base lips specification: see project_box_rectangle() |

| lips_cover | 2 | Cover lips specification: see project_box_rectangle() |

| lips_sides | 9 | Sides lips specification: see project_box_rectangle() |

| mode_proj_box | 0 | Mode for project_box_rectangle() module |

| mode_rounding | 2 | Enclosure rounding mode: {0|1|2} |

| mode_sides | 0 | Enclosure sides mode |

| multi_board_offset | 0 | Multi-riser inter board offset |

| posts | undef | Post instances for sides, base and cover: see project_box_rectangle() |

| posts_base | [[3, [-1, -1], [7.5, 7.5], 0, undef, undef, undef, [2, 180, undef, 0.166667]], [3, [-1, 1], [7.5, -7.5], 270, undef, undef, undef, [2, 180, undef, 0.166667]], [3, [1, -1], [-7.5, 7.5], 90, undef, undef, undef, [2, 180, undef, 0.166667]], [3, [1, 1], [-7.5, -7.5], 180, undef, undef, undef, [2, 180, undef, 0.166667]]] | Post instances base only: see project_box_rectangle() |

| posts_base_conf | [0, [undef, undef, undef, undef, undef, undef, undef, undef]] | Post configuration base: [mode, default]: see project_box_rectangle() |

| posts_cover | [[3, [-1, -1], [7.5, 7.5], 0, undef, undef, undef, [2, 180, undef, 0.166667]], [3, [-1, 1], [7.5, -7.5], 270, undef, undef, undef, [2, 180, undef, 0.166667]], [3, [1, -1], [-7.5, 7.5], 90, undef, undef, undef, [2, 180, undef, 0.166667]], [3, [1, 1], [-7.5, -7.5], 180, undef, undef, undef, [2, 180, undef, 0.166667]]] | Post instances cover only: see project_box_rectangle() |

| posts_cover_conf | [0, [undef, undef, undef, undef, undef, undef, undef, undef]] | Post configuration cover: [mode, default]: see project_box_rectangle() |

| posts_sides | [[2, [-1, -1], [7.5, 7.5], 180, undef, undef, undef, [4, 120, undef, 0.166667]], [2, [-1, 1], [7.5, -7.5], 90, undef, undef, undef, [4, 120, undef, 0.166667]], [2, [1, -1], [-7.5, 7.5], 270, undef, undef, undef, [4, 120, undef, 0.166667]], [2, [1, 1], [-7.5, -7.5], 0, undef, undef, undef, [4, 120, undef, 0.166667]]] | Post instances sides only: see project_box_rectangle() |

| posts_sides_conf | [0, [undef, undef, undef, undef, undef, undef, undef, undef]] | Post configuration sides: [mode, default]: see project_box_rectangle() |

| rb_min_clearance | 0 | Riser board minimum bottom clearance |

| rib_pcb_gap | 0.5 | Rib removal gap for PCIE and riser board PCB |

| ribs | 0 | Enclosure wall rib specification: see project_box_rectangle() |

| rounding | 6.75 | Enclosure corner rounding radius |

| shapes_base | undef | Enclosure base shapes instances: see project_box_rectangle() |

| shapes_cover | undef | Enclosure cover shapes instances: see project_box_rectangle() |

| shapes_sides | undef | Enclosure side shapes instances: see project_box_rectangle() |

| space_add_edge1 | 0 | Space to add to riser edge-1 |

| space_add_edgen | 0 | Space to add to riser edge-n |

| space_add_height | 0 | Space to add to enclosure height |

| space_add_length | 0 | Space to add to riser end length |

| space_min_height | 0 | Enclosure minimum interior height |

| space_min_length | 0 | Enclosure minimum interior length |

| verb_proj_box | 0 | Verbosity for project_box_rectangle() |

| walls | undef | Enclosure interior walls: see project_box_rectangle() |

| wth | 2 | Enclosure minimum wall thickness |

| e | data type | default value | parameter description |

|---|---|---|---|

| 0 | decimal | thickness | |

| 1 | decimal | tab-boarders (width addition) | |

| 2 | decimal | screw hole diameter | |

| 3 | decimal-list-4 | decimal | tab rounding | |

| 4 | decimal-list-4 | decimal | tab rounding modes | |

| 4 | decimal-list-5 | decimal | dovetail configuration: see joint2d_dovetail() t |

| name | schema |

|---|---|

| clamps_base | [[configuration, instances]] |

| e | data type | default value | parameter description |

|---|---|---|---|

| 0 | decimal-list-2 | wire hole size [w, h] | |

| 1 | decimal-list-2 | zip-tie hole size [w, h] | |

| 2 | decimal-list-3 | clamp envelope size [w, h, d] | |

| 3 | datastruct | tunnel configuration: see clamp_zt_1p() tunnel | |

| 4 | decimal-list3-list-4 | vr [clamp, wire, tunnel] | |

| 5 | integer-list3-list-4 | vrm [clamp, wire, tunnel] |

| e | data type | default value | parameter description |

|---|---|---|---|

| 0 | integer-list-2 | enclosure side [w, l] | |

| 1 | decimal | clamp rotate [z] | |

| 2 | integer | clamp align [d] | |

| 3 | decimal-list-2 | clamp move [w, l] | |

| 4 | datastruct | side passage hole |

| e | data type | default value | parameter description |

|---|---|---|---|

| 0 | binary | enabled | |

| 1 | decimal | vertical cut extension | |

| 2 | datastruct | wall cone: see clamp_cg() cone |

| e | data type | default value | parameter description |

|---|---|---|---|

| 0 | decimal-list-4 | edge cut insets: [bb, bt, ft, fb] | |

| 1 | decimal-list-4 | cut rounding: [bb, bt, ft, fb] | |

| 2 | integer-list-4 | cut rounding mode: [bb, bt, ft, fb] |

See the documentation for project_box_rectangle() under the section for hole configuration for more details on hole specification.

See the documentation for project_box_rectangle() under the section for shape configuration for more details on shape specification.

See the documentation for project_box_rectangle() under the section for post configuration for more details on post specification.

Integer value is binary encoded.

| b | description |

|---|---|

| 0 | Add mount tab shelves |

| 1 | Hull adjacent-slot mount tab shelf |

| 2 | Hull removal of adjacent-slot connector windows |

| 3 | Hull removal of adjacent-slot ribs from wall |

| 4 | Hull removal of adjacent-slot bracket slide-down space |

| 5 | Enable enclosure side cutting |

| 6 | Cut enclosure front (positive side) |

| 7 | Cut enclosure rear (negative side near bracket) |

| 8 | Remove ribs on front enclosure wall for riser PCB |

| 9 | Remove ribs on front enclosure wall for PCIE card PCB |

Definition at line 962 of file pcie_expansion.scad.